Published on Sep 16, 2019

We put forward design and development of a novel, low complexity processor in memory (PIM) architecture for image and video compression. By integrative a Novel processing element with SRAM, bandwidth is improved and latency is greatly reduced.

Through this paper we present PIM design techniques for reduced power, area, and complexity for rapid deployment and reduced cost. A design methodology is presented and followed by an analysis of the processing element performance and capabilities.

The architecture executes a discrete cosine and wavelet transforms achieving higher output and area consumption is very less

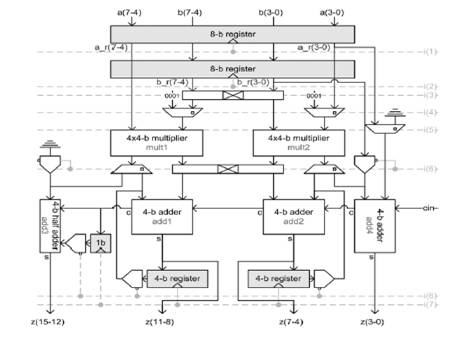

The proposed architecture utilizes a multiplier-based application specific processor (ASP). Specifically, the ASP is constructed to compute key algorithms and operations essential to image and video processing in order to minimize the complexity and the power consumption, delivering high throughput at very lowcost. The focus in this paper is mainly on the datapath design

VHDL

Simulation: modelsim5.8c

Synthesis: Xilinx 9.1